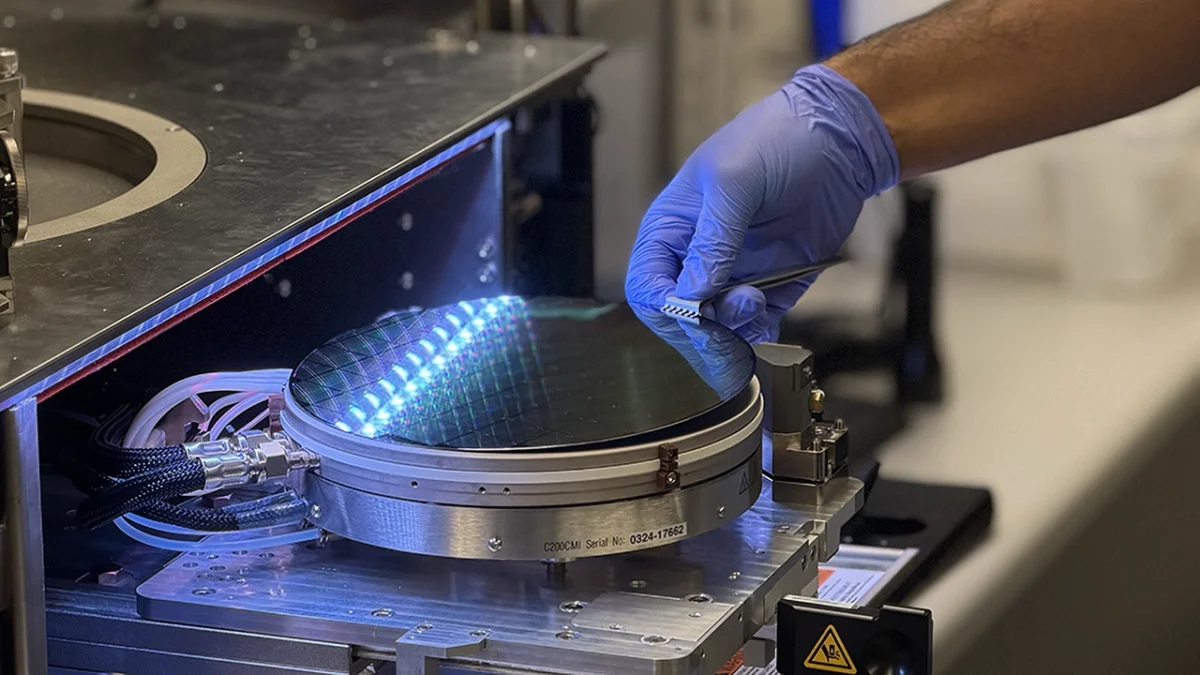

تراشه سه بعدی با معماری عمودی و عملکرد ۱۰ برابری ساخته شد

مهندسان آمریکایی تراشهای سهبعدی ساختهاند که با معماری عمودی، سرعت پردازش و بهرهوری انرژی را برای هوش مصنوعی بهطور چشمگیر افزایش میدهد.

به گزارش سرویس اخبار فناوری جهانی مگک، این تراشهٔ که با معماری چندلایه طراحی شده است، در آزمایشهای سختافزاری و شبیهسازیها، عملکردی در حدود ۱۰ برابر بهتر از تراشههای دوبعدی متداول نشان داده و توجه پژوهشگران و فعالان صنعت را به خود جلب کرده است. توسعهدهندگان این فناوری معتقدند که چنین جهشی، میتواند نیازهای پردازشی نسلهای آیندهٔ سامانههای هوش مصنوعی را پاسخ دهد.

بر اساس توضیحات تیم پژوهشی، برخلاف تراشههای امروزی که ساختاری تخت و دوبعدی دارند، اجزای کلیدی این تراشهٔ جدید بهصورت عمودی روی هم قرار گرفتهاند. این طراحی، تراشه را به ساختمانی چندطبقه شبیه میکند که در آن، سیمکشیهای عمودی نقش آسانسورهای پرسرعت را ایفا میکنند و امکان جابهجایی سریع و همزمان حجم عظیمی از دادهها را فراهم میسازند. به گفتهٔ مهندسان، همین ویژگی باعث شده است تا محدودیتهای سنتی انتقال داده در تراشههای تخت تا حد زیادی برطرف شود.

چگالی بالای اتصالات عمودی و ترکیب دقیق واحدهای حافظه و محاسبات، از مهمترین تفاوتهای این تراشه با نمونههای مرسوم به شمار میرود. این ساختار به تراشه اجازه میدهد از گلوگاههایی عبور کند که سالها مانع افزایش محسوس کارایی در طراحیهای دوبعدی شده بودند. یکی از این گلوگاهها، مشکلی است که مهندسان از آن با عنوان «دیوار حافظه» یاد میکنند.

برای مطالعه: ساخت تراشههای الکترونیکی با تکنیک جدید چاپ سهبعدی

«دیوار حافظه» یک اصطلاح فنی در معماری کامپیوتر است و به محدودیتی بنیادی در سرعت پردازش اشاره دارد.دیوار حافظه زمانی رخ میدهد که سرعت واحد پردازش بسیار بیشتر از سرعت دسترسی به حافظه باشد. در این حالت، پردازنده توان انجام محاسبات را دارد، اما بهدلیل کندی انتقال داده از حافظه، مجبور میشود منتظر بماند.

در تراشههای دوبعدی رایج، اجزا روی یک سطح تخت واحد قرار دارند و حافظه بهصورت محدود و پراکنده در دسترس است. در نتیجه، دادهها باید از مسیرهای طولانی و شلوغ عبور کنند. از آنجا که واحدهای محاسباتی بسیار سریعتر از سرعت جابهجایی داده عمل میکنند و حافظهٔ کافی نیز در نزدیکی آنها وجود ندارد، سامانه اغلب در انتظار دریافت اطلاعات میماند. این ناهماهنگی میان سرعت پردازش و انتقال داده، یکی از چالشهای اصلی معماریهای کنونی محسوب میشود.

سوبهاسیش میترا، استاد مهندسی برق و علوم رایانه در دانشگاه استنفورد و پژوهشگر اصلی مقالهای که این تراشه را معرفی میکند، اعلام کرد که این دستاورد، درهای یک دورهٔ تازه از تولید و نوآوری در صنعت تراشه را میگشاید. او تأکید کرد که پیشرفتهایی از این جنس، برای دستیابی به بهبودهای بسیار بزرگ در عملکرد سختافزاری که سامانههای آیندهٔ هوش مصنوعی به آن نیاز دارند، ضروری است.

بخوانید: تراشه XRING O2 شیائومی قلب تپنده سری 17S خواهد بود

اگرچه آزمایشگاههای دانشگاهی در سالهای گذشته نمونههایی از تراشههای سهبعدی آزمایشی ساخته بودند، اما این نخستین بار است که یک تراشهٔ سهبعدی، هم افزایش عملکردی واضح را نشان میدهد و هم در یک کارخانهٔ تجاری تولید میشود. این موضوع، از نگاه پژوهشگران، گامی مهم در مسیر تجاریسازی فناوریهای پیشرفتهٔ نیمههادی به شمار میرود.

تاتاگاتا سریمانی، استاد یار مهندسی برق و مهندسی رایانه در دانشگاه کارنگی ملون و نویسندهٔ ارشد این پژوهش، توضیح داد که ادغام عمودی حافظه و محاسبه، امکان انتقال سریعتر حجم بسیار بیشتری از اطلاعات را فراهم میکند. او این فرآیند را به عملکرد آسانسورهای یک برج بلند تشبیه کرد که به تعداد زیادی از افراد اجازه میدهند بهطور همزمان بین طبقات جابهجا شوند.

در توسعهٔ این تراشهٔ سهبعدی، مهندسانی از دانشگاه استنفورد، دانشگاه کارنگی ملون، دانشگاه پنسیلوانیا و مؤسسهٔ فناوری ماساچوست با شرکت فناوری اسکایواتر همکاری داشتهاند.

انتایج آزمونهای اولیه نشان میدهد که این نمونهٔ اولیه، در حال حاضر عملکردی حدود چهار برابر بهتر از تراشههای دوبعدی مشابه ارائه میدهد. شبیهسازی نسخههای پیشرفته تر که شامل لایههای بیشتری از حافظه و واحدهای محاسباتی هستند، به بهبودهای حتی بزرگتری اشاره دارد. طبق اعلام تیم پژوهشی، برخی طراحیها در بارهای کاری واقعی هوش مصنوعی، ازجمله بارهایی برگرفته از مدل متنباز LLaMA متعلق به متا ، تا دوازده برابر افزایش کارایی را نشان دادهاند.

علاوه بر افزایش سرعت، پژوهشگران معتقدند که این معماری جدید میتواند به بهبود چشمگیر بهرهوری انرژی نیز منجر شود. آنها اعلام کردهاند که این طراحی، مسیر واقعبینانهای را برای بهبود ۱۰۰ تا ۱۰۰۰ برابری در شاخص انرژی–تأخیر یا EDP فراهم میکند. کوتاهشدن مسیر جابهجایی داده و افزایش تعداد مسیرهای عمودی، امکان دستیابی همزمان به توان عملیاتی بالاتر و مصرف انرژی کمتر را فراهم میسازد.

بخوانید: احتمال استفاده از تراشههای اینتل در مدلهای غیر پروی آیفون ۲۱

رابرت ام. رادوِی، استاد یار دانشگاه پنسیلوانیاو یکی از نویسندگان این مطالعه، هشدار داد که ترکیب «دیوار حافظه» و «دیوار کوچکسازی» میتواند مانعی جدی برای پیشرفت آیندهٔ پردازش باشد. او تأکید کرد که تیم پژوهشی با ادغام فشردهٔ حافظه و منطق و ساخت عمودی با چگالی بسیار بالا، بهطور مستقیم به این چالش پاسخ داده است؛ رویکردی که به گفتهٔ او، دنیای محاسبات را به شهری متراکم و عمودی شبیه میکند که در آن، کارایی بیشتری در فضای کمتر به دست میآید.